前言

说实话,我平时是真的很讨厌上这门数字逻辑电路的课的,对于计算机专业的学生来说这门课美名其曰给你提升思维,其实P用没有,反而耽搁学习计算机核心课程时间,我是真的不想浪费时间在这门课上面。但是没办法啊,考试还得考,做个实验在那发呆反而更加浪费时间。所以我想着写个解析记录下来方便我期末复习,于是就诞生了本篇文章。

接下来我们将通过74LS161芯片解决如何定制不同进制的计数器问题解决这个问题有两个办法:①:预置法。②:反馈复位法

解决方法

预置法

所谓预置方法呢,意思就是说我预先设定好一个初始值,当我的数到了要进位的时候呢,直接强制输入那个初始值作为下一个数进行输出

反馈复位法

反馈复位法则是通过一个芯片自带的重置引脚对值进行初始化处理。

我们对比着两个方法可以发现,这两个方法都需要知道我计数器什么时候进位,不同的就是一个通过预设的值的引脚进行强制输入初始化,另一个通过系统的重置引脚进行初始化。

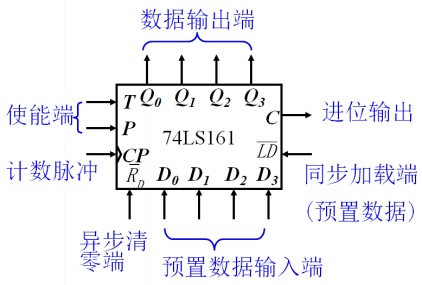

74LS161芯片图

这里简单介绍一下:$D_0 $~$D_3$是芯片的数据预置输入端,你可以通过对$D_0 $~$D_3$进行高低电平设计来设置芯片的输出初始值。这个芯片的输出是直接通过8421法进行十进制输出的,比如 0 1 0 1 从左到右依次对应8 4 2 1 那我们把它们加起来,十进制对应的数就是1+0+4+0=5,再比如0 1 0 0那对应8 4 2 1 加起来的十进制数就是等于0 + 0 +4 +0=4。这里的$D_0$~$D_3$的顺序限定死的,$D_0$代表二进制的最低位,也就是8 4 2 1 中的 1位置,依次推下去,$D_3$就对应二进制的最高位,也就是 8 4 2 1 的8的位置

$Q_0$~$Q_3$代表了数据的输出端,$Q_0$~$Q_3$的下标0~3依次与D中的下标对应,即$D_0对应Q_0,.......D_3对应Q_3$。所以Q系列的引脚作用是用于接入到数码管中用于数字的显示。

ET (Toggle Enable)和EP(Preset Enable)是芯片的使能端,就是对应图中的T和P,当EP和ET一起被置为高电平时,芯片将允许计数器在时钟脉冲到达时对内部计数值进行增量更新。它通常与ET一起控制计数器是否可以进行计数操作。

CP全称"Clock Pulse",其作用在于:当输入的脉冲发生 上升沿(从低电平跳变到高电平),且当计数器的其他使能条件,如使能输入(如EP和ET)和清除输入引脚$\overline R_D$,都处于适当状态时,CP信号的每次上升沿都会使计数器的内容增加1(以二进制方式计数)。总而言之它就是作为一个脉冲输入的信号

$\overline R_D$是异步清零端,当它处于低电平的时候,计数器的输出将重置到初始值状态

$\overline {LD}$全称load,是同步加载端,当其处于低电平的时候,下一次的脉冲上升沿的时候,计数器的Q端输出端将强制输出为D端对应的预置数据。

C 全称"Carry Out",其实就是进位的输出信号,当在达到计数器的最大值后发出一个电信号

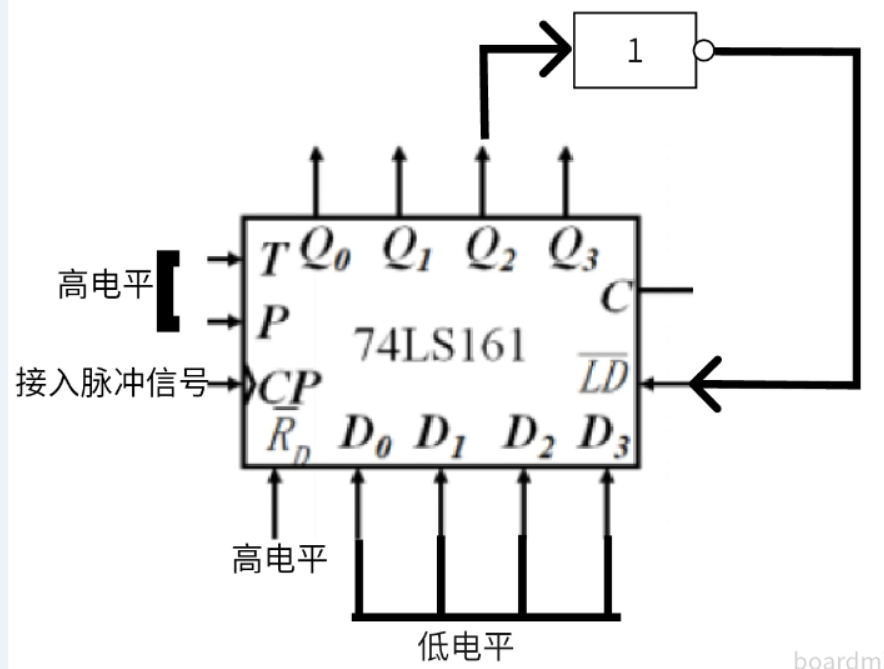

预置法设计五进制计数器

我们说过预置法的意思就是说我预先设定好一个初始值,当我的数到了要进位的时候呢,直接强制输入那个初始值作为下一个数进行输出。简化一下这句话:我们需要一个设置初始值、进位检测的装置,外加一个强制写入初始值到计数器的装置。

所以我们只要有个设置初始值、进位检测、强制写入初始值到计数器的装置就完成了我们的计数器设计

设置初始值

根据我们上文提到的74LS161芯片图我们的引脚的定义说明,我们可以知道预置初始值这个功能我们的D端引脚就能做到。要注意D端引脚8421编码,且$D_0$对应最低位,也就是8421编码中1的位置,依次类推,$D_3$对应8421的8的位置。 接下来我举个例子:比如我们要预设十进制4,4利用8421法我们可以知道其编码为0100,那我们只要$D_2$给高电平,其他D引脚低电平即可。

进位检测

要设计的一个进位检测,那我们就要问问自己什么时候需要进位????本题是五进制,五进制的规律是逢五进一,且刚好$\overline {LD}$端引脚的功能就是当其处于低电平的时候,下一次的脉冲上升沿将会强制D端的预设值写入Q端的输出值,根据这一特性我们想当Q输出十进制4的时候,这个4有什么特点就可以了,4的二进制是0100,可以发现其它三位都是0,且我们数字是不会超过5的,也就是说0111、0101、0110等这些情况根本就不会存在,也就是说对于4来着它的二进制0100从左往右数第二位($Q_2$),也就是说当$Q_2$为1的时候我们就可以告诉$\overline {LD}$:你该准备准备进位了!!。但是接收到低电平信号才会运行,那我们就直接给接个非门不就完事了。

强制写入初始值到计数器

的引脚功能刚好可以帮我们实现

实现效果如下图:

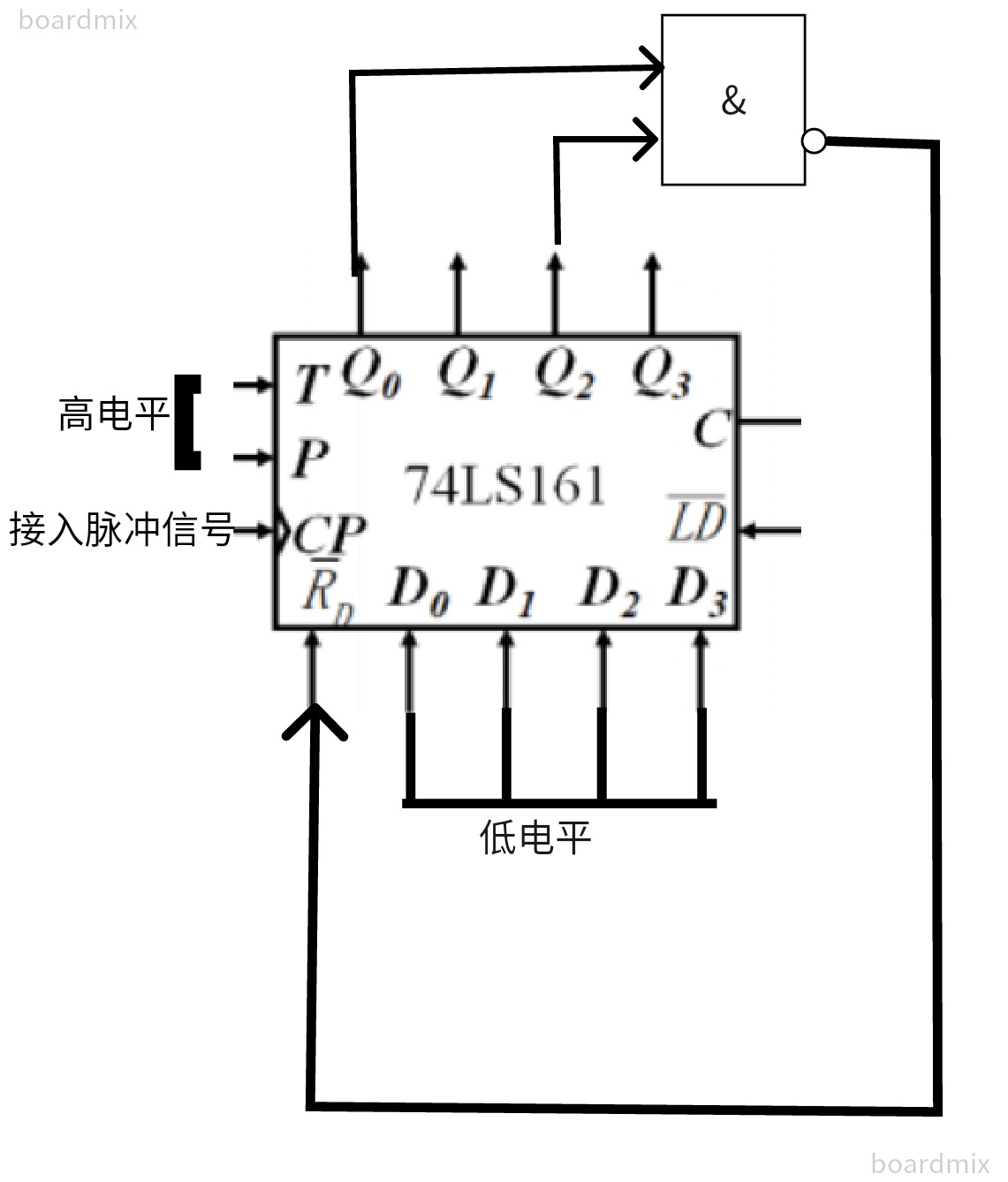

反馈复位法设计五进制计数器

反馈复位法和的预置法的区别无非就是反馈复位法用的是$\overline R_D$,而预置法则是用的$\overline {LD}$引脚强制输入预置数的功能。不过区别还是有的, $\overline {LD}$是对下一次脉冲的时候才会生效,所以我们预置法的时候我们需要分析的是十进制数4分解成2进制的时候的特点,而反馈复位法用的是引脚$\overline R_D$,这个引脚是实时生效的,根本不需要等到下一次,所以我们要分析十进制数5的,我们将其拆解成二进制数:0101。0 1 0 1分别对应$Q_3 、Q_2、Q_1、Q_0$。由于$\overline R_D$是实时生效,且遇到低电平生效,那我们同理直接给$Q_2、Q_0$接到一个与非门即可,其同时为1的时候出0,让$\overline R_D$生效即可。

据此我们就可以画出如下的设计图:

总结一下

其实设计的核心就在于找到进位的特征,然后据此给芯片设计发送一个进位信号即可。一般对于某某N进制,如果采用预置法那我们就要找到N-1对于的二进制,找到这个二进制的特征,然后发送进位信号给$\overline {LD}$即可,如果采用反馈复位法直接去找N对于的二进制即可,因为反馈复位法的$\overline R_D$是实时更新数字的,而非像$\overline {LD}$需要等到下一次脉冲的上升沿才会强制写入预置数。

版权所有:浪浪山

文章标题:数字逻辑电路74LS161四位二进制同步计数器剖析

文章链接:https://www.langlangshan.cloud/?post=5

本站文章均为原创,未经授权请勿用于任何商业用途

文章标题:数字逻辑电路74LS161四位二进制同步计数器剖析

文章链接:https://www.langlangshan.cloud/?post=5

本站文章均为原创,未经授权请勿用于任何商业用途

收藏

扫描二维码,在手机上阅读

推荐阅读: